FPGA

- Flip-chip pin grid array не треба да се поврзува со FPGA. За повеќе видете пакување на интегрални кола.

Field-programmable gate array (FPGA) е полупроводникчки уред кој може да се конфигурира од страна на корисникот или дизајнерот по произведувањето. FPGA може да биде програмиран со употреба на дијаграми на логички кола или со изворен код преку јазик за опис на хардверот HDL за да се специфицира како треба да работи чипот. Може да се употреби за да се имплементира било која логичка функција што едно интегрално коло со специфична задача ASIC може да ја изврши, но можноста за ажурирање на функционалноста по доставата овозможува предности за многу апликации.[1]

FPGA содржи програмабилни логички компоненти наречени "логички блокови", и хиерархија реконфигурабилни меѓуповрзаности што овозможуваат на блоковите да бидат "ожичени заедно". Логичките блокови може да бидат конфигурирани да извршуваат комплексни комбинациони функции, или едноставни логички порти како на пример И и XOR. Кај повеќето FPGA уреди, логичките блокови вклучуваат мемориски елементи.[1]

Историјат

[уреди | уреди извор]FPGA индустријата изникнува од програмабилната read only меморија (PROM) и програмабилните логички уреди (PLD). PROM и PLD ја имале можноста да бидат програмирани во сериско производство или конфигурирани по производството, но сепак програмабилната логика била ожичена меѓу логичките порти.[2]

Xilinx Соосновачите, Рос Фриман и Бернард Вондершмит, ја измислиле прватата комерцијална теренско програматорска низна порта во 1985 – XC2064.[3] XC2064 имала програматорски порти и програматорски меѓуповрзаности помеѓу порти, тоа бил почетокот на нова технологија на пазарот.[4] XC2064 содржела 64 конфигурациони логички порти (CLB), со три влеза прегледни таблици (LUT).[5]

Некои од индустриските основни концепти и технологии за програматорски логички низи, порти и логички блокови сепатентирани на името на Дејвид В. Пејџ и Луверн Р. Петерсно во 1985.[6][7]

Во доцните 1980-ти Naval Surface Warfare Department ја почнал експериментот предложен од Стив Каселман за развој на компјутер којшто ќе вклучува 600.000 репрограматорски порти. Проектот бил испешен и системот бил патентиран во 1992.[2]

Xilinx продолжил со неоспорен развој и брз растеж од 1985 до средината на 1990-тите, кога конкуренцијата надминала. Веќе во 1993, Actel имал околу 18% од пазарот.[4]

1990-тите биле експлозивен период за FPGA, во поглед на софистицираноста и волуменот на производство. Во раните 1990-ти, FPGA главно се користеле во телекомуникациите и мрежните поврзаности. Кон крајот на декадата, FPGA веќе изградиле и пат кон потрошувачите и индустриските апликативности.[8]

FPGA се прославиле во 1997, кога Адријан Томпсон употребил технологија на генетски алгоритам и FPGA за да создаде уред за распознавање на глас. Томпсоновиот алгорита овозможил низа од 64 x 64 ќелии коритсјки Xilinx FPGA чип да одлучи која е потребната конфигурација за извршување на гласовни распознавачки задачи.[2]

Модерен развој

Скорешните трендови зеле курс на за однесување на архитектурниот пристап чекор понапред комбинирајки ги логичките блокови и меѓуповрзаности на традиционален FPGA со приложни микрообработувачи и поврзани периферии за да формират комплетен "системна програмабилен чип". Оваа работа е огледало на архитектурата на Рон Перлоф и Хана Поташ од Burroughs Advanced Systems Group која комбинирала реконфигурабилна ЦПЕ архитектура на единичен чип наречен SB24. Таа работа била завршена во 1982. Примери ваква хибридна технологија може да биде видена и кај Xilinx Virtex-II PRO и Virtex-4 уредите, коишто вклучуваат еден или повеќе PowerPC обработувачи приложени во the FPGA логичка фабрика. Atmel FPSLIC е друг таков уред, кој користи AVR процесор во комбинација со Atmel програмабилна логичка архитектура.

Алтернативен приод користејки hard-macro обработувачи за да се искористи "софт" процесор јадра коишто се имплементирани во FPGA логика. (Види "Софт Обработувачи", подолу).

Како што е претходно споменато, доста модерни FPGA ја имаат возможноста да бидат репрограмирани во "run time," и ова води до идејата за реконфигурабилно пресметување или реконфигурабилни ситеми — ЦПЕ коишто се реконфигурираат самите себе за да се прилагодат кон извршување задача. Mitrion Virtual Processor од Mitrionics е пример за реконфигурабилен софт процесор, имплементиран на FPGA. Сепак, не поддржува динамичка реконфигурација во runtime, но се адаптира себеси кон специфична програма.

Порти

- 1987: 9,000 порти, Xilinx[4]

- 1992: 600,000, Naval Surface Warfare Department[2]

- Рани 2000-ти: милиони [8]

Големина на пазарот

- 1985: Прва комерзијална FPGA технологија измислена од страна на Xilinx[4]

- 1987: $14 милиони[4]

- ~1993: >$385 милиони[4]

- 2005: $1.9 билиони[9]

- 2010 estimates: $2.75 billion [9]

FPGA дазиајн почетоци

FPGA компарација

[уреди | уреди извор]Историски гледано, FPGA се бавни, помалки ефикасни по моќност и главно постигнуваат помалку функционалности од нивните ASIC соперници. Комбинацијата од зафатнина, подобрување на производството, развој и истражување, како и влезно-излезните можности на новите суперкомпјутери ја затвориле празнината меѓу ASIC и FPGA.[13]

Основната разлика помеѓу CPLD и FPGA е архитектурна. CPLD има на некој начин рестриктивна структура состоејќи се од еден или повеќе пробрамабилни збир-од-производ логички низи поддржувајќи релативно мал број на тактирани регистри. Резултатот од ова е помалку флексибилност, со предноста што временските задоцнувања се попредвидливи и односот логика-меѓуповрзаност е поголем. Во FPGA архитектурата од друга страна од друга страна преовладуваат меѓуповрзаностите. Ова ги прави далеку пофлексибилни, но исто така и далеку покомплексни за дизајн.

Примена

[уреди | уреди извор]FPGA се применуваат во дигитална обработка на сигнали, софтверски-дефинирано радио, космички и одбранбени системи, моделирање на ASIC, медицински слики, компјутерска визија, распознавање на глас, криптографија, биоинформатика, емулација на компјутерски хардвер и друго.

Архитектура

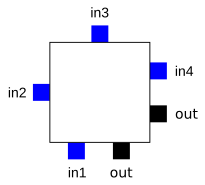

[уреди | уреди извор]Нај застапената FPGA архитектура[14] се состои од низ од конфигурабилни логички блокови (CLB), В/И падови, и рутни канали. Генерално, сите рутнимканали имаат иста тежина (број жици). Повеќе В/И падови може да се совпаднат со бројот редови или колони на низот.

Апликационо колко мора да биде мапирано во FPGA со адекватни ресурси. Додека бројот CLB и И/В кои се потребни се лесно определиви од дисајнот, бројот патеки кој е потребен може значајно да варира дури и кај дизајни со иста логика. Неискористените патеки ја накачуваат цената (и ги намалуваат перформанситеe) од делот којшто не бенифицира, FPGA произведувачите се обидуваат да достават онолку патеку колку што би биле потребни на дизајнерите во однос на искористената.

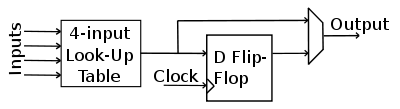

Класичен FPGA логичен блок се состои од 4 влеза lookup table (LUT), и flip-flop.

Има само еден излез, регистер или нерегистриран излез. Логичкиот блок има 4 влеза и клок влез.

Секој влез е достапен од една страна на логичкиот блок, додека излезот може да се поврзува со рутни патеки и на истиот блокк или соседен.

Аналогно, В/И пад може да се поврзува на било кој од жичните сегменти на адаптабилните канали до него. FPGA рутирањето е несегментирано. Секој жичен сегмент троши само еден логички блок пред да заврши во свич кутија. Било кога хоризонтален или вертикален канал да се препокрие, има свич ккутија. Во оваа архитектура, кога жица влезе во свич кутија има три свича коишто овозможуваат да се поврзува со дуги три жици.

Наводи

[уреди | уреди извор]- ↑ 1,0 1,1 FPGA Architecture for the Challenge

- ↑ 2,0 2,1 2,2 2,3 „History of FPGAs“. Архивирано од изворникот на 2007-04-12. Посетено на 2009-03-25.

- ↑ Peter Clarke, EE Times, "Xilinx, ASIC Vendors Talk Licensing Архивирано на 11 мај 2008 г.." 22 јуни 2001. Retrieved 10 февруари 2009.

- ↑ 4,0 4,1 4,2 4,3 4,4 4,5 Funding Universe. “Xilinx, Inc.” Retrieved 15 јануари 2009.

- ↑ Clive Maxfield, Programmable Logic DesignLine, "Xilinx unveil revolutionary 65nm FPGA architecture: the Virtex-5 family Архивирано на 25 декември 2009 г.. 15 мај 2006. Retrieved 5 февруари 2009.

- ↑ Google Patent Search, "Re-programmable PLA". Retrieved 5 февруари 2009.

- ↑ Google Patent Search, "Dynamic data re-programmable PLA". Retrieved 5 февруари 2009.

- ↑ 8,0 8,1 Clive Maxfield, book, "The Design Warrior's Guide to FPGAs".Published by Elsevier, 2004. ISBN 0-7506-7604-3, 9780750676045. Retrieved 5 февруари 2009

- ↑ 9,0 9,1 Dylan McGrath, EE Times, "FPGA Market to Pass $2.7 Billion by '10, In-Stat Says Архивирано на 15 јуни 2011 г.". 24 мај 2006. Retrieved 5 февруари 2009.

- ↑ Narinder Lall, eASIC Corporation, "FPGA Judgment Day:Rise of Second Generation Structured ASICs Архивирано на 14 декември 2010 г.. March, 2008. Retrieved 5 февруари 2009.

- ↑ 11,0 11,1 Dylan McGrath, EE Times, "Gartner Dataquest Analyst Gives ASIC, FPGA Markets Clean Bill of Health Архивирано на 14 јули 2007 г.". 13 јуни 2005. Retrieved 5 февруари 2009.

- ↑ Virtex-4 Family Overview

- ↑ Bob Pencek, Industrial Embedded Systems, "Reconfigurable Application-Specific Computing: How Hybrid Computer Systems using FPGAs are Changing Signal Processing Архивирано на 22 март 2009 г.". No Date. Retrieved 5 февруари 2009.

- ↑ http://www.eecg.toronto.edu/~vaughn/challenge/fpga_arch.html

| „FPGA“ на Ризницата ? |

|